半導体ナノワイヤとは、太さがナノメートルオーダーの半導体細線で、トランジスタ・発光素子・太陽電池など、様々な応用へ向けて研究が行われています。本研究室では、特に次世代集積回路におけるトランジスタ応用へ向けて、半導体ナノワイヤにおけるキャリア(電子・正孔)輸送の物理に焦点を当てた研究を行っています。

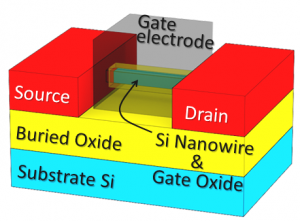

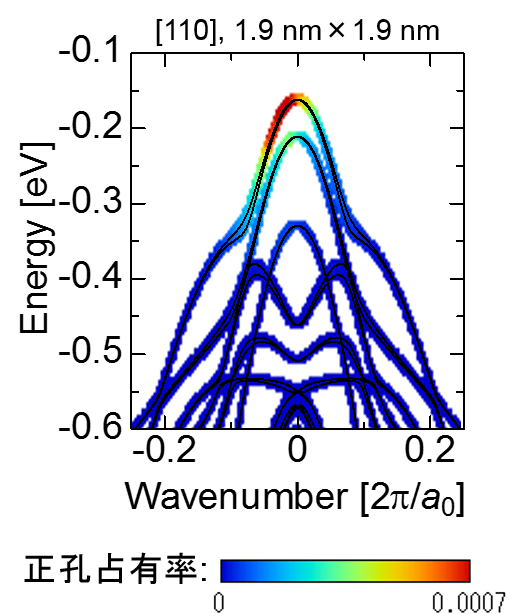

トランジスタ(MOSFET)においてナノワイヤを用いることの利点としては、まず、極めて細いナノワイヤをチャネルとして、その周りをゲート電極で完全に囲い込むことにより、ゲートによるチャネル電位の制御性を高められるという点があります。これにより、既存のデバイス構造(平面型FET、FinFET等)では実現不可能な、急峻なオン・オフの切り替え特性(これができないと消費電力・発熱が増大してしまいます)と究極的な微細化(微細化は基本的には性能向上に繋がります)の両立が可能となります。加えて、ナノワイヤの太さが数ナノメートルといったキャリアの波長を下回るサイズになると、キャリアを量子力学的波動としてナノワイヤ内に閉じ込めることでその振る舞いを大きく変化させることができます。例えば、Ge(ゲルマニウム)における正孔の輸送有効質量は通常0.2 m0程度(m0は電子の静止質量)ですが、適切なナノワイヤ形状を用いることでバンド構造をうまく「設計」すれば、0.08 m0程度まで軽くできると理論的に予測されています(軽い有効質量は輸送特性の向上に繋がります)。このような量子閉じ込めが生じると、キャリアと格子振動(フォノン)との相互作用、構造の不完全性によるキャリアの散乱、キャリアのトンネル効果等もナノワイヤの構造に応じて変化します。本研究室では、このようなナノワイヤにおけるキャリア輸送の物理を、量子力学や(非平衡)統計力学に基づき理解し、高性能・低消費電力なナノワイヤトランジスタの実現につなげることを目指しています。

以下に、本研究室で取り組んできた主なテーマを示します。

- SiナノワイヤMOSFETの作製とその電気的特性の評価、理論的バンド構造との比較

- ナノワイヤにおけるバンド構造の原子論的手法による計算

- ナノワイヤMOSFETのキャリア輸送特性の理論計算

- ナノワイヤにおけるキャリア散乱の定式化、キャリア移動度の計算

(発表論文の例)

H. Yoshioka et al., “Bandgap shift by quantum confinement effect in <100> Si-nanowires derived from threshold-voltage shift of fabricated metal-oxide-semiconductor field effect transistors and theoretical calculations,” J. Appl. Phys., vol. 109, 064312 (2011).

N. Morioka et al., “Quantum-confinement effect on holes in silicon nanowires: Relationship between wave function and band structure,” J. Appl. Phys., vol. 109, 064318 (2011).

S. Mori et al., “Orientation and shape effects on ballistic transport properties in gate-all-around rectangular germanium nanowire nFETs,” IEEE Trans. Electron Devices, vol. 60, 944 (2013).

H. Tanaka et al., “Modeling of surface roughness scattering in nanowires based on atomistic wave function: Application to hole mobility in rectangular germanium nanowires,” Phys. Rev. B, vol. 93, 155303 (2016).

-

ナノワイヤMOSFETの

模式図 -

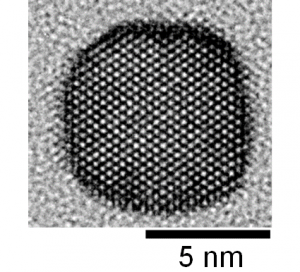

本研究室で作製したシリコンナノワイヤの断面透過型電子顕微鏡像

-

シリコンナノワイヤにおける価電子帯構造と高電界(50 kV/cm)印加時の分布関数の計算結果